#### Universidade de Santiago de Compostela

Departamento de Electrónica e Computación Centro de Investigación en Tecnoloxías da información (CITIUS)

#### PhD Dissertation

### NEW HARDWARE SUPPORT FOR TRANSACTIONAL MEMORY AND PARALLEL DEBUGGING IN MULTICORE PROCESSORS

Author:

Lois Orosa Nogueira

Phd Advisors:

Javier Díaz Bruguera Elisardo Antelo Suárez

Santiago de Compostela, June 2013

**Javier Díaz Bruguera**, Profesor Catedrático de Universidade da Área de Arquitectura e Tecnoloxía de Computadores da Universidade de Santiago de Compostela

Elisardo Antelo Suárez, Profesor Titular de Universidade da Área de Arquitectura e Tecnoloxía de Computadores da Universidade de Santiago de Compostela

#### FAN CONSTAR:

Que a memoria titulada NEW HARDWARE SUPPORT FOR TRANSACTIONAL MEMORY AND PARALLEL DEBUGGING IN MULTICORE PROCESSORS foi realizada por D. Lois Orosa Nogueira baixo a nosa dirección no Departamento de Electrónica e Computación e no Centro Singular de Investigación en Tecnoloxías da Información (CITIUS) da Universidade de Santiago de Compostela, e constitue a Tese que presenta para optar ao grado de Doutor pola Universidade de Santiago de Compostela.

Santiago de Compostela, Xuño 2013

Javier Díaz Bruguera

Codirector da tese

Elisardo Antelo Suárez

Codirector da tese

Lois Orosa Nogueira Autor da tese

Everything that can be invented has been invented.

Charles H. Duell, U.S. patent office, 1899

It would appear that we have reached the limits of what it is possible to achieve with computer technology, although one should be careful with such statements, as they tend to sound pretty silly in 5 years.

John Von Neumann, 1949

O verdadeiro heroísmo está en transformar os desexos en realidades e as ideas en feitos.

Castelao

## **Acknowledgements**

Five years ago I gave a radical turn to my life: I quit a stable job in a private company to start this research adventure. The way was long, it had ups and downs, but at the end, it was worth it. It was an invaluable experience that changed and marked me forever, personally and professionally, and I would not have been able to do it alone. It is at this point that I want to thank all the people that made this thesis possible.

First of all, and the most important, I want to thank my advisors Elisardo Antelo and Javier Bruguera. They trusted in me from the beginning of this adventure, and we start and finish this trip together. Without them, this thesis would simply not be possible. Their constant support was essential to finish it, as also the advices and motivating talks of Elisardo. Thank you very much.

To Professor Josep Torrellas, who supervised my work in my stay in the University of Illinois at Urbana-Champaign, and to all the members of his group for their kind welcome. Special thanks to Shanxiang Qi and Norimasa Otsuki for the good work environment and the intriguing discussions.

To the people of IBM R&D research Lab in Haifa for their friendly welcome during my HiPEAC internship there. My acknowledgements goes specially to Olga Golovanevsky, Marina Biberstein and Bilha Mendelson for their daily support and the motivating work made there.

To Recore Systems, specially to Gerard Rauwerda, for trusting me to perform a very engaging project during my HiPEAC internship, and to John Donker, Jordy Potman and Eduard Fernández for their every day support and knowledge, which enriched my stay.

I also want to express my gratitude with the funding institutions. The work related to this PhD thesis was partially supported by the Spanish Ministry of Science and Education under Project TIN2007-67537-C03-01. I also wish to thank the European Network of Excellence on

High Performance and Embedded Architecture and Compilation (HiPEAC) for the funding that allowed me to perform my internships in Haifa and Enschede during my thesis period.

Fora do ámbito profesional, tamén quero agradecer á xente que estivo ao meu arredor todos estes anos deixando un recordo indeleble da miña etapa de tese e servindo como válvula de escape cando mais o necesitaba. Grazas aos meus amigos, compañeiros de piso, compañeiros de departamento, á xente que fixo mais levadeiras as miñas estancias no estranxeiro e a esas persoas especiais que pasaron pola miña vida. Grazas a Xacobo&Marta, Marcos, Jose, Rodrigo, Rafa, Antón, Manolo, Nerea&Manolo, Ricardo, Fran, Saul e Ángela por tódolos momentos vividos en Compostela; grazas a Antón por todo o tempo e aventuras compartidas; grazas a Carlos, Manolo e Yolanda por ser os compañeiros de piso perfectos; grazas a Ale, Juli, Emi, Nino, Aitor, Miguel, Gabi, Víctor, Jose, Manu&Patri, Paula, Tania, Deborah e demais tropa viguesa polos momentos vividos nas nosas xuntanzas; grazas aos compañeiros de ESF por tanta implicación e rebeldía; grazas a Cris, Fer, Enrique(s) e demais xente do departamento por compartir preocupacións, sufrimentos e festas; thanks to Norimasa for making my stay at Urbana-Champaign very special; thanks to Vladimir, Waldemar and Per for making my stay in Haifa an experience that I will never forget; thanks to Jarkko, Eduard, Aria-Lena and Stefania for being my happiness during my stay in Enschede; grazas a Sandra por axudarme a tomar a decisión de comezar esta aventura, e por apoiarme nos meus primeiros anos de tese; grazas a Sol por estar aí nesta última etapa; e grazas a moitos outros que non nomeo pero que igualmente foron parte fundamental para o meu desenvolvemento persoal e profesional.

Quero dar tamén as grazas á miña familia, sobre todo aos meus primos Marcos, Telmo, Paula&Alberto, Marta, Lucía, Laura, Alex, e Noa, e moi especialmente aos meus pais Suso e Carmiña, por apoiarme sempre. Ademais quero ter un recordo moi especial coa miña avoa Dolores. Por último, quero dar tamén as gracias ao meu irmán Adrián, a Maca, e ao novo recén chegado, o meu sobriño Ían.

Moitas grazas a todos! Thank you very much! Santiago de Compostela, June 2013

## **Contents**

| Li | st of I | Figures       |                                                 | 1  |

|----|---------|---------------|-------------------------------------------------|----|

| Li | st of T | <b>Fables</b> |                                                 | 5  |

| Pr | eface   |               |                                                 | 7  |

| 1  | Intr    | oductio       | n                                               | 11 |

|    | 1.1     | Paralle       | el Architectures                                | 12 |

|    |         | 1.1.1         | Why Parallel Architectures?                     | 12 |

|    |         | 1.1.2         | Levels of Parallelism                           | 13 |

|    |         | 1.1.3         | Shared Memory Multicore Processors              | 14 |

|    | 1.2     | Paralle       | el Programming                                  | 18 |

|    |         | 1.2.1         | Data Communication                              | 20 |

|    |         | 1.2.2         | Problem Decomposition                           | 21 |

|    | 1.3     | Paralle       | el Programming Issues in Shared Memory          | 22 |

|    |         | 1.3.1         | Synchronization                                 | 22 |

|    |         | 1.3.2         | Debugging Concurrency Bugs in Parallel Programs | 26 |

|    | 1.4     | Transa        | actional Memory (TM)                            | 29 |

|    |         | 1.4.1         | Basic Concepts                                  | 30 |

|    |         | 1.4.2         | Hardware Transactional Memory (HTM)             | 34 |

|    |         | 1.4.3         | Software Transactional Memory (STM)             | 42 |

|    |         | 1.4.4         | Hybrid Transactional Memory (HyTM)              | 44 |

|    |         | 1.4.5         | Other Speculative Techniques                    | 45 |

|    | 1.5     | Backg         | round on Signatures                             | 45 |

|    |         | 151           | Fundamentals                                    | 46 |

xii Contents

|   |      | 1.5.2    | True Bloom Signature                      | 49 |

|---|------|----------|-------------------------------------------|----|

|   |      | 1.5.3    | Parallel Bloom Signature                  | 51 |

|   |      | 1.5.4    | Other Signature Implementations           | 52 |

|   | 1.6  | Conclu   | usions                                    | 54 |

| 2 | Eval | uation   | Methodology                               | 55 |

|   | 2.1  | Simula   | ator Framework                            | 55 |

|   |      | 2.1.1    | Simics and GEMS                           | 56 |

|   |      | 2.1.2    | PIN                                       | 58 |

|   |      | 2.1.3    | Rochester STM                             | 59 |

|   |      | 2.1.4    | SESC                                      | 61 |

|   | 2.2  | Bench    | marks                                     | 61 |

|   |      | 2.2.1    | SPLASH-2                                  | 61 |

|   |      | 2.2.2    | STAMP                                     | 65 |

|   |      | 2.2.3    | PARSEC                                    | 67 |

|   |      | 2.2.4    | EigenBench                                | 69 |

|   |      | 2.2.5    | Other Benchmarks                          | 70 |

|   | 2.3  | Conclu   | usions                                    | 70 |

| 3 | Red  | ucing th | ne Use of Signatures in a HTM system      | 71 |

|   | 3.1  | System   | n Architecture                            | 72 |

|   |      | 3.1.1    | Managing Transactional Writes with CFM-TM | 72 |

|   |      | 3.1.2    | Replacement Algorithm                     | 76 |

|   |      | 3.1.3    | Commit and Abort Actions                  | 76 |

|   |      | 3.1.4    | Limitations                               | 77 |

|   |      | 3.1.5    | Interactions between CFM-TM and LogTM-SE  | 77 |

|   | 3.2  | Signat   | ures                                      | 82 |

|   | 3.3  | Evalua   | ation                                     | 82 |

|   |      | 3.3.1    | System Model                              | 83 |

|   |      | 3.3.2    | Workloads                                 | 83 |

|   |      | 3.3.3    | Results                                   | 84 |

|   | 3.4  | Relate   | d Work                                    | 89 |

|   | 3.5  | Conclu   | usion                                     | 90 |

Contents xiii

| 4 | Tole | rating A | Asymmetric Data Races with a Hardware Signature Module            | 91  |

|---|------|----------|-------------------------------------------------------------------|-----|

|   | 4.1  | Asymi    | metric Data Races in Real World                                   | 92  |

|   | 4.2  | PACM     | IAN: Tolerating Asymmetric Data Races                             | 93  |

|   |      | 4.2.1    | Overview of the Idea                                              | 94  |

|   |      | 4.2.2    | Basic Pacman Protocol                                             | 96  |

|   |      | 4.2.3    | Interaction with Cache                                            | 97  |

|   |      | 4.2.4    | Advanced Pacman Protocol to Avoid Deadlocks and Stalls            | 100 |

|   | 4.3  | Imple    | mentation Issues                                                  | 103 |

|   |      | 4.3.1    | Other Issues                                                      | 105 |

|   | 4.4  | Evalua   | ation                                                             | 107 |

|   |      | 4.4.1    | Experimental Setup                                                | 107 |

|   |      | 4.4.2    | Characterization                                                  | 109 |

|   |      | 4.4.3    | Overheads                                                         | 109 |

|   |      | 4.4.4    | Handling Bugs                                                     | 113 |

|   | 4.5  | Relate   | d Work                                                            | 115 |

|   |      | 4.5.1    | Software Proposals for Asymmetric Races                           | 115 |

|   |      | 4.5.2    | Other Related Work                                                | 116 |

|   | 4.6  | Conclu   | usions                                                            | 117 |

| 5 | Imp  | lementi  | ing a Flexible Hardware Signature Module                          | 119 |

|   | 5.1  | FlexSi   | g: Implementing Flexible Hardware Signatures                      | 120 |

|   |      | 5.1.1    | Allocation Algorithm                                              | 122 |

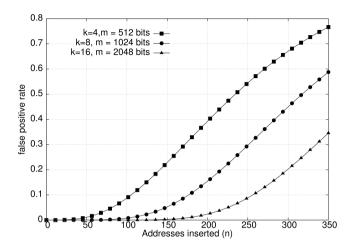

|   |      | 5.1.2    | Influence of the Bloom Filters Release on the False Positive Rate | 125 |

|   |      | 5.1.3    | Software Interface                                                | 125 |

|   |      | 5.1.4    | Register Grouping                                                 | 126 |

|   |      | 5.1.5    | FlexSig Overflow and Fault Tolerance                              | 127 |

|   | 5.2  | Imple    | mentation Issues                                                  | 128 |

|   | 5.3  | Evalua   | ation in a TM System                                              | 129 |

|   |      | 5.3.1    | Unified signatures: Simplifying FlexSig Implementation in TM      | 130 |

|   |      | 5.3.2    | Experimental Setup                                                | 131 |

|   |      | 5.3.3    | Configuration                                                     | 132 |

|   |      | 5.3.4    | Results                                                           | 134 |

|   | 5.4  | Relate   | d Work                                                            | 138 |

|   | 5.5  | Concl    | usions                                                            | 139 |

xiv Contents

| 6  | Asy    | mmetri   | c Allocation in a Flexible Signature Module               | 141 |

|----|--------|----------|-----------------------------------------------------------|-----|

|    | 6.1    | Asymı    | metric Policies                                           | 142 |

|    |        | 6.1.1    | Asymmetric Allocation Algorithm with Two Priority Classes | 143 |

|    |        | 6.1.2    | Asymmetric Algorithms for TM                              | 145 |

|    | 6.2    | Impler   | mentation Issues                                          | 149 |

|    |        | 6.2.1    | Placement of FlexSig in a Multicore Processor             | 149 |

|    |        | 6.2.2    | Hardware Implementation in a TM System                    | 149 |

|    |        | 6.2.3    | Basic Elements                                            | 150 |

|    |        | 6.2.4    | Allocation Implementation: Arithmetic Calculations        | 152 |

|    |        | 6.2.5    | Control Logic                                             | 155 |

|    | 6.3    | Evalua   | ation for a TM System                                     | 158 |

|    |        | 6.3.1    | Experimental Setup                                        | 158 |

|    |        | 6.3.2    | Evaluation for the PCIN Priority Class                    | 159 |

|    |        | 6.3.3    | Evaluation for Multiple PCIN Priority Classes             | 163 |

|    |        | 6.3.4    | Evaluation for Combined PCOUT and PCIN Priority Classes   | 164 |

|    |        | 6.3.5    | FlexSig with a High Number of Threads                     | 166 |

|    |        | 6.3.6    | Signature Size Comparison                                 | 166 |

|    | 6.4    | Relate   | d Work                                                    | 168 |

|    |        | 6.4.1    | Comparing Asymmetric FlexSig and ASYM signatures          | 169 |

|    | 6.5    | Conclu   | asion                                                     | 171 |

| Co | onclus | sions an | d Future Work                                             | 173 |

| Re | esumo  | da Tes   | e                                                         | 177 |

| Bi | bliog  | raphy    |                                                           | 187 |

# **List of Figures**

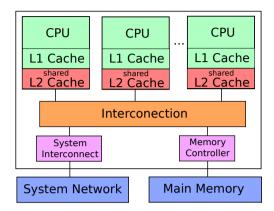

| Fig. 1.1 | Basic strucure of a shared memory multicore processor                          | 15 |

|----------|--------------------------------------------------------------------------------|----|

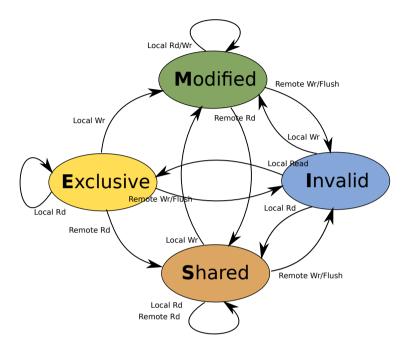

| Fig. 1.2 | · · · · · · · · · · · · · · · · · · ·                                          | 17 |

| ·        |                                                                                |    |

| Fig. 1.3 | Dinning philosophers problem                                                   | 22 |

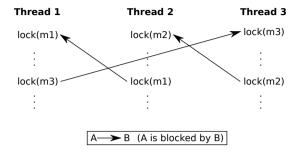

| Fig. 1.4 | Deadlock scenario                                                              | 25 |

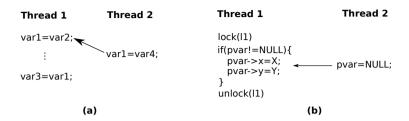

| Fig. 1.5 | Examples of data races                                                         | 27 |

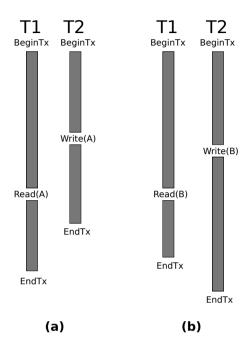

| Fig. 1.6 | Eager-Lazy conflict detection example                                          | 32 |

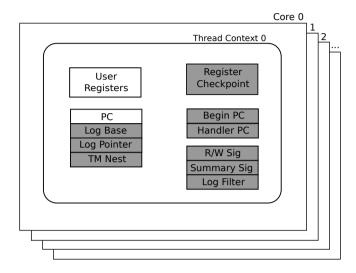

| Fig. 1.7 | LogTM-SE hardware organization                                                 | 37 |

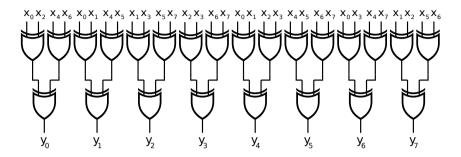

| Fig. 1.8 | Example of $H_3$ hash function. The inputs are defined by the $H_{example}$ of |    |

|          | Equation 1.4                                                                   | 48 |

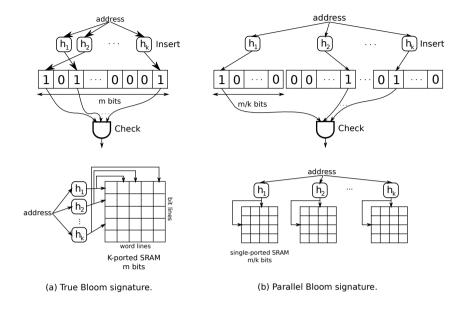

| Fig. 1.9 | Bloom signatures                                                               | 49 |

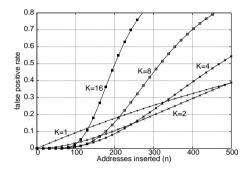

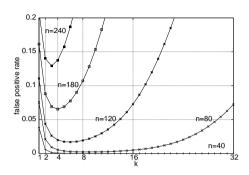

| Fig. 1.1 | O False positive rate for parallel Bloom filter with $m = 1024$                | 51 |

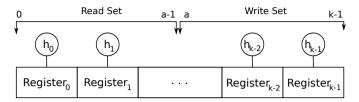

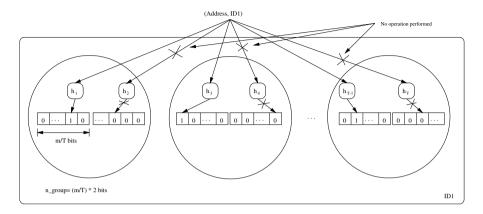

| Fig. 1.1 | 1 High level scheme of the ASYM signature                                      | 53 |

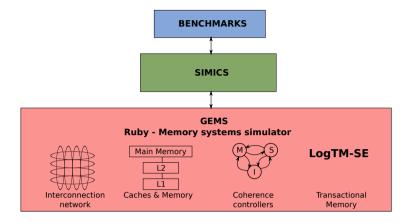

| Fig. 2.1 | SIMICS+GEMS overview                                                           | 57 |

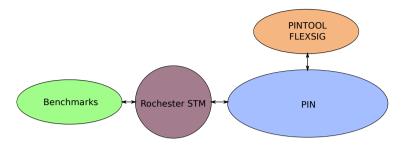

| Fig. 2.2 | Simulation framework of Chapters 5 and 6                                       | 59 |

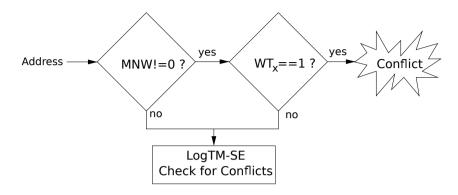

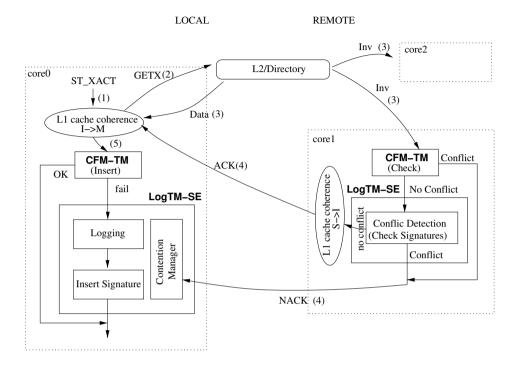

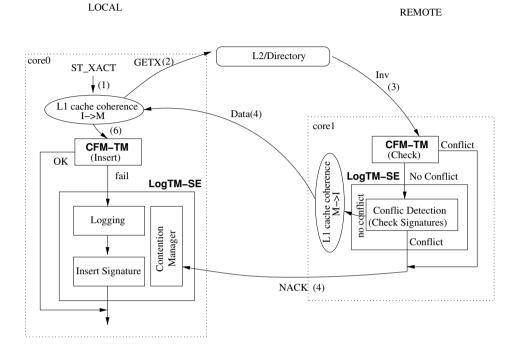

| Fig. 3.1 | Check for conflicts in a LogTM-SE system with the CFM-TM filter                | 74 |

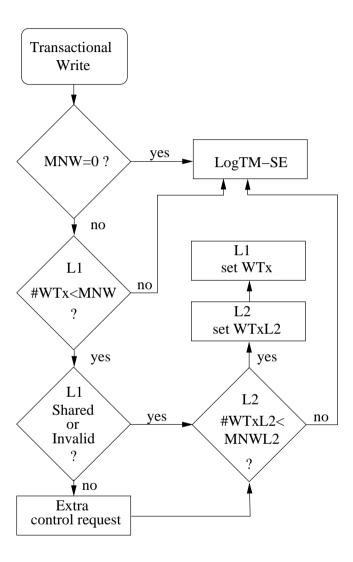

| Fig. 3.2 | Transactional write action in the LogTM-SE system using the CFM-TM filter.     | 75 |

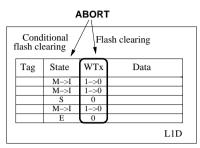

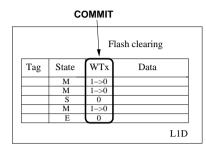

| Fig. 3.3 | Abort and commit actions                                                       | 77 |

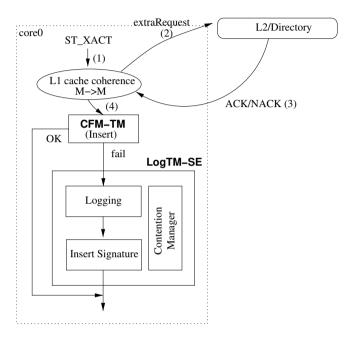

| Fig. 3.4 | Interaction between CFM-TM and LogTM-SE in a transactional store miss          | 78 |

| Fig. 3.5 | Interaction between CFM-TM and LogTM-SE in a transactional store miss          | 80 |

| Fig. 3.6 | Interaction between CFM-TM and LogTM-SE in a transactional store hit           | 81 |

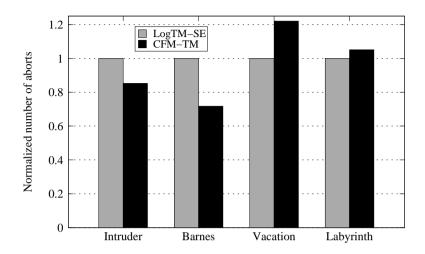

| Fig. 3.7 | Normalized number of aborts                                                    | 84 |

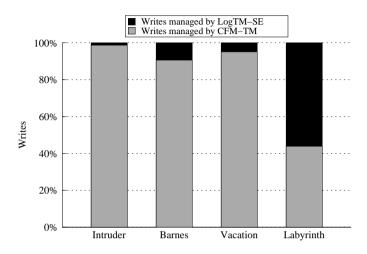

| Fig. 3.8 | Write management distribution.                                                 | 85 |

2 List of Figures

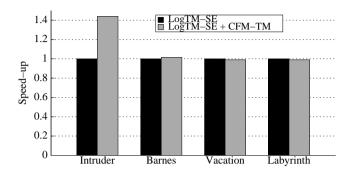

| Speed-up of LogTM-SE + CFM-TM                                                    | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

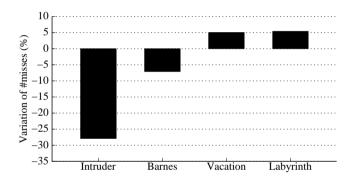

| Variation of L1 cache misses when the CFM-TM is activated                        | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

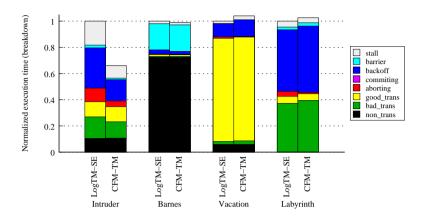

| Normalized breakdown of execution cycles                                         | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

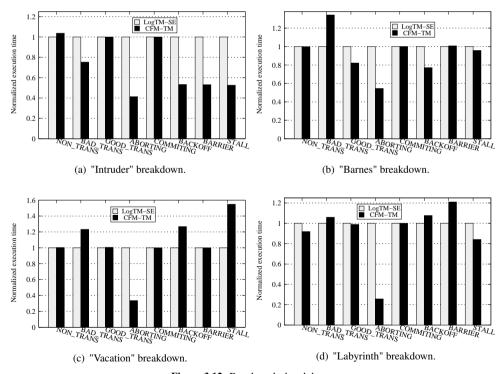

| Benchmarks breakdown                                                             | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

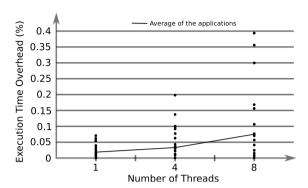

| Examples of asymmetric data races where the unsafe thread can proceed            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (OK) or not (NOT OK)                                                             | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

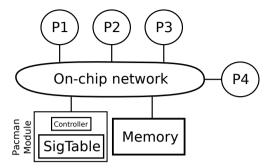

| Overview architecture of Pacman                                                  | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

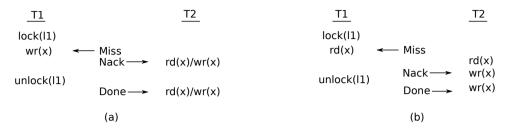

| Examples to understand the Pacman's operation                                    | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Examples to understand Cache State Prior to Entering the Critical Section        | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Examples of data race bugs which lead to deadlock                                | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Breaking atomicity due to false sharing                                          | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

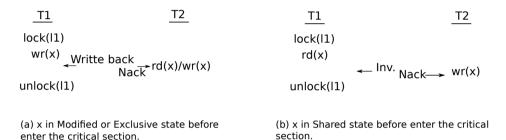

| Pacman Implementation                                                            | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

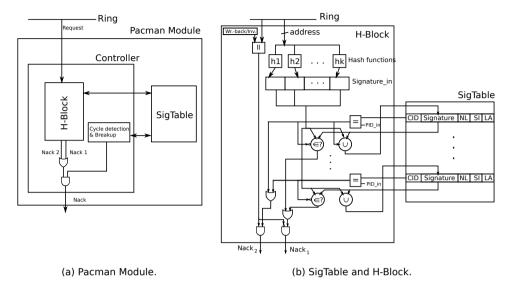

| Execution time overhead of Pacman                                                | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| An asymmetric race in "Bodytrack" benchmark                                      | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| An asymmetric race in "FMM" benchmark                                            | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Block diagram of FlexSig                                                         | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

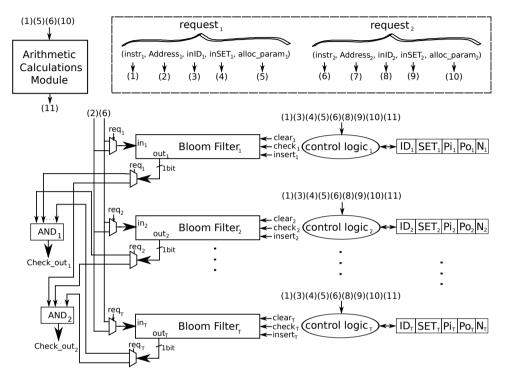

| FlexSig module architecture                                                      | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Insertion, check and deallocation request in FlexSig                             | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example of the symmetric allocation algorithm of FlexSig                         | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example of conventional signatures used in a system with a maximum of 16         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| simultaneous signature requesters                                                | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| False positive rate in <i>FlexSig</i> for different signature sizes              | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example of register grouping                                                     | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

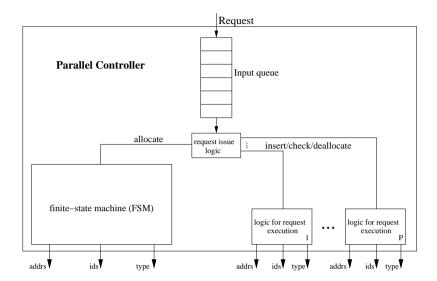

| Parallel controller implementation                                               | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

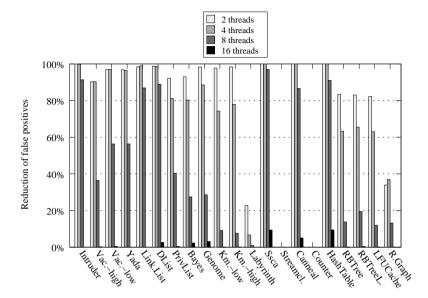

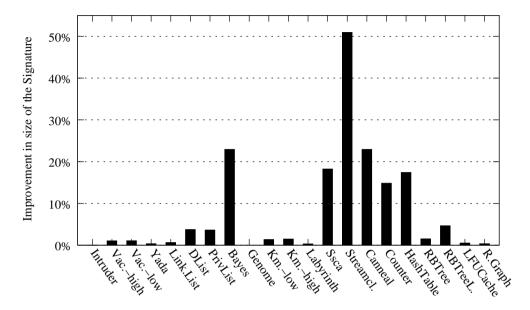

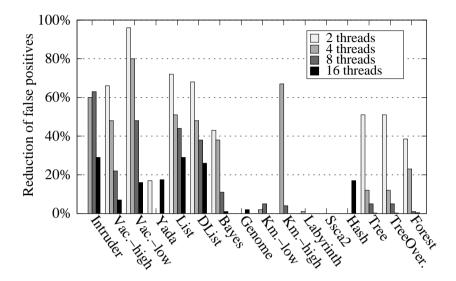

| Percentage of decrease of the absolute number of false positives in FlexSig-     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| conf1 compared with conventional signatures for all benchmarks                   | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

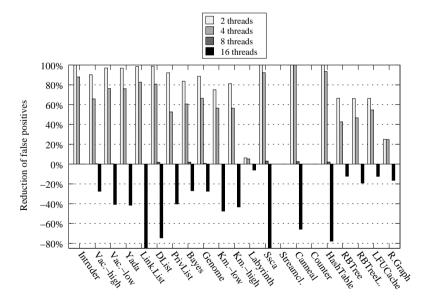

| Percentage of decrease of the absolute number of false positives in FlexSig-     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| conf2 compared with conventional signatures for all benchmarks                   | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Increment of the signature size in FlexSig-conf2                                 | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example of an asymmetric R/W allocation algorithm                                | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example of an asymmetric allocation algorithm based on transaction identifier. 1 | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                  | Normalized breakdown of execution cycles. Benchmarks breakdown.  Examples of asymmetric data races where the <i>unsafe thread</i> can proceed (OK) or not (NOT OK).  Overview architecture of Pacman.  Examples to understand the Pacman's operation.  Examples to understand Cache State Prior to Entering the Critical Section.  Examples of data race bugs which lead to deadlock.  Breaking atomicity due to false sharing.  Pacman Implementation.  Execution time overhead of Pacman.  An asymmetric race in "Bodytrack" benchmark.  An asymmetric race in "FMM" benchmark.  Block diagram of <i>FlexSig</i> .  FlexSig module architecture.  Insertion, check and deallocation request in <i>FlexSig</i> .  Example of the symmetric allocation algorithm of <i>FlexSig</i> .  Example of conventional signatures used in a system with a maximum of 16 simultaneous signature requesters.  False positive rate in <i>FlexSig</i> for different signature sizes.  Example of register grouping.  Parallel controller implementation.  Percentage of decrease of the absolute number of false positives in <i>FlexSig-conf1</i> compared with conventional signatures for all benchmarks.  Percentage of decrease of the absolute number of false positives in <i>FlexSig-conf2</i> compared with conventional signatures for all benchmarks.  Increment of the signature size in <i>FlexSig-conf2</i> . |

List of Figures 3

| Fig. 6.3  | Example of an asymmetric allocation algorithm combining PCOUT and                     |     |

|-----------|---------------------------------------------------------------------------------------|-----|

|           | PCIN priority classes                                                                 | 149 |

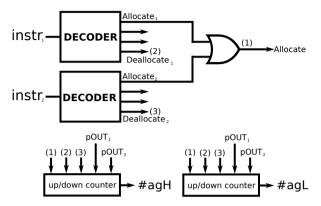

| Fig. 6.4  | The basic <i>FlexSig</i> elements in a two-way implementation (issue 2 instructions). | 150 |

| Fig. 6.5  | Generation of the allocation signal and the update of the registers that count        |     |

|           | the number of transactions.                                                           | 153 |

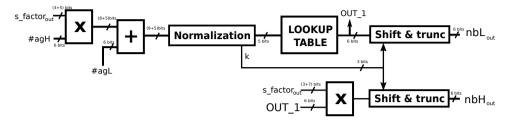

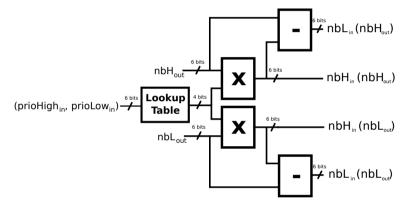

| Fig. 6.6  | Calculation of the maximum number of Bloom filters for high and low                   |     |

|           | priority transactions                                                                 | 154 |

| Fig. 6.7  | Calculation of the maximum number of Bloom filters per signature,                     |     |

|           | depending on its priority and the priority of the transaction which it belongs.       | 154 |

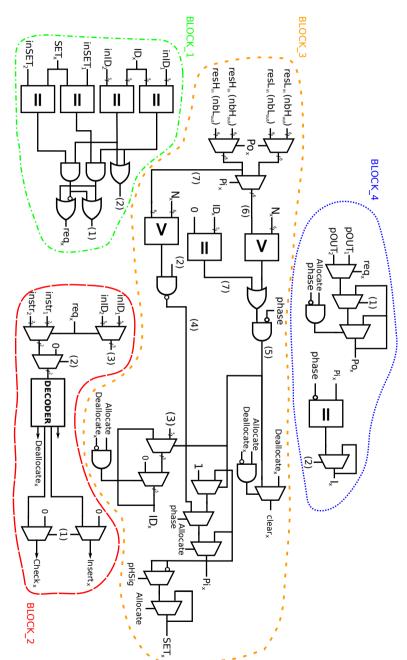

| Fig. 6.8  | Control logic for each Bloom filter                                                   | 156 |

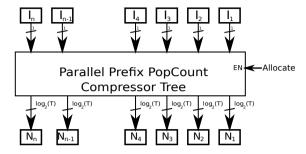

| Fig. 6.9  | Generation of the $N_x$ values with a parallel prefix popcount compressor tree.       | 157 |

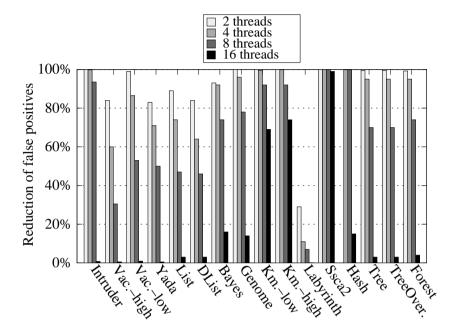

| Fig. 6.10 | Percentage of decrease of false positives in symmetric FlexSig                        | 161 |

| Fig. 6.11 | Percentage of decrease on false positives in FlexSig with asymmetric                  |     |

|           | allocation policies (PCIN priority class)                                             | 162 |

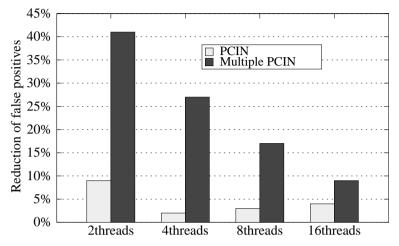

| Fig. 6.12 | Percentage of reduction of false positives for single PCIN priority and for           |     |

|           | Multiple (one per transaction) PCIN priorities                                        | 164 |

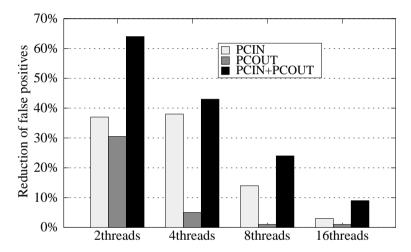

| Fig. 6.13 | Percentage of decrease on false positives in FlexSig implementing priorities          |     |

|           | for PCIN priority class, for PCOUT priority class, and combining both PCIN            |     |

|           | and PCOUT priority classes                                                            | 165 |

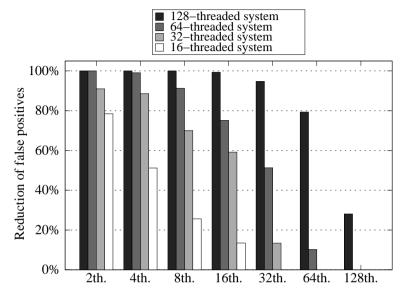

| Fig. 6.14 | Percentage of decrease of false positives in asymmetric FlexSig (PCIN                 |     |

|           | priority class) with up to 128 threads                                                | 167 |

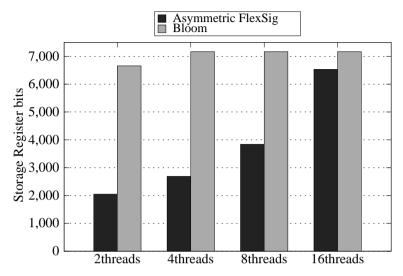

| Fig. 6.15 | Number of bits required for registers in asymmetric FlexSig (PCIN priority            |     |

|           | class) and Bloom signatures                                                           | 168 |

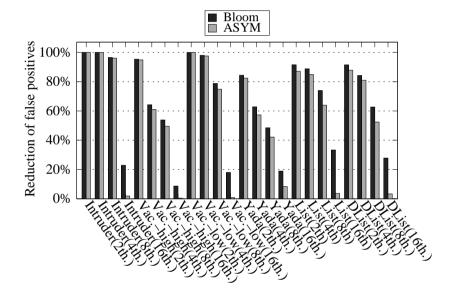

| Fig. 6.16 | Percentage of decrease of false positives in asymmetric FlexSig                       |     |

|           | implementing the PCIN priority class, compared with Bloom and ASYM                    |     |

|           | signatures                                                                            | 170 |

## **List of Tables**

| Tabla 2.1 | System configuration                                                                 | 58  |

|-----------|--------------------------------------------------------------------------------------|-----|

| Tabla 2.2 | RSTM implementations                                                                 | 60  |

| Tabla 2.3 | Benchmarks                                                                           | 62  |

| Tabla 3.1 | Workload characteristics                                                             | 83  |

| Tabla 3.2 | Benchmark inputs                                                                     | 83  |

| Tabla 3.3 | Signature's size configuration with and without CFM-TM                               | 84  |

| Tabla 4.1 | Real examples of harmful asymmetric data races                                       | 93  |

| Tabla 4.2 | Size of the SigTable's fields                                                        | 104 |

| Tabla 4.3 | Default architecture parameters                                                      | 108 |

| Tabla 4.4 | SigTable parameters                                                                  | 108 |

| Tabla 4.5 | Characteristics of the critical sections (CS) in the applications                    | 110 |

| Tabla 4.6 | Quantification of the overheads                                                      | 112 |

| Tabla 5.1 | Benchmark Inputs                                                                     | 131 |

| Tabla 5.2 | Benchmark set A, characterization with 16 threads                                    | 132 |

| Tabla 5.3 | Benchmark set B, characterization with 16 threads                                    | 133 |

| Tabla 5.4 | Configuration used with unified signatures                                           | 133 |

| Tabla 5.5 | Benchmark Set A. False positives comparison (in %) for Unified Signatures.           | 134 |

| Tabla 5.6 | Benchmark Set B. False positives comparison (in %) for Unified Signatures.           | 134 |

| Tabla 6.1 | Values calculated by <i>FlexSig</i> in the examples of the Figures 6.1, 6.2 and 6.3. | 146 |

| Tabla 6.2 | Benchmark Inputs                                                                     | 159 |

| Tabla 6.3 | Size of the read and write sets for different benchmarks                             | 159 |

6 List of Tables

| Tabla 6.4  | Configuration of the signatures used                                         | 160 |

|------------|------------------------------------------------------------------------------|-----|

| Tabla 6.5  | $s\_factor_{in}$ ( $prioHigh_{in} prioLow_{in}$ ) for 2, 4, 8 and 16 threads | 161 |

| Tabla 6.6  | Priorities used for single and multiple PCIN priorities                      | 163 |

| Tabla 6.7  | <i>s_factor</i> used to evaluate both PCOUT and PCIN priority classes        | 165 |

| Tabla 6.8  | $s\_factor_{in}$ used to evaluate the scalability of $FlexSig.$              | 166 |

| Tabla 6.9  | Configuration of <i>FlexSig</i> and Bloom signatures                         | 167 |

| Tabla 6.10 | Number of Bloom filters for read and write set in ASYM signatures            | 170 |

## **Preface**

In the multicore era, parallel programming is becoming a must for general purpose programmers. However, the parallelization of programs is not intrinsically intuitive and prone to errors. To face these drawbacks, new tools have arisen to make this task easier by providing new programming models and debugging tools. Usually, these new tools add complexity that needs to be addressed with hardware support to achieve a good performance. Transactional Memory and data race detection are two of the most popular.

Transactional Memory (TM) is a software abstraction to make parallel programming easier, by providing an abstraction less prone to errors than locks. TM provides an speculative synchronization mechanism to the programmer, who has to enclose critical sections in transactions which will be executed atomically and in isolation by the TM system. Furthermore, transactions are executed in parallel and speculatively, so it is pretty common to use hardware support to accelerate the system.

A data race occurs when two or more threads access the same shared variable without the proper synchronization. Data races can produce errors which are very difficult to debug, because it is usual that the error manifests itself much later than the actual race is produced. Therefore, to efficiently detecting these bugs has become very important, and also for these tools, it is not strange to use hardware support to not degrade the performance of the system.

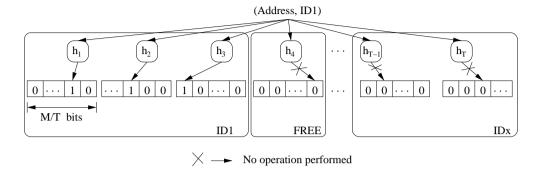

Among the hardware resources for accelerating this kind of tools, one of the most generally used in research papers, and therefore, with a lot of potential to be included in future general purpose processors, are signatures. Signatures are a fixed piece of hardware that can host an unbounded number of addresses in a bounded space. To do that, each address is hash encoded and inserted in the signature, which may produce aliasing among address. This leads to the possibility of reporting false positives when the signature checks for the ownership of an address. However, it never reports false negatives.

8 Preface

This thesis contributes with new hardware support for TM and data race detection in multicore processors. The hypothesis to build this thesis are:

- Hardware signatures are not optimized for the many applications and tools that use them (very different ones in the same system).

- Signatures can be used in a large number of applications related with parallel programming of multicore processors, and some of them are unexplored.

- Signatures are a promising hardware resource because of their efficiency, but they have drawbacks that have not been explored: they are not flexible to adapt to the different requirements of the applications and tools that may require them in a multicore processor.

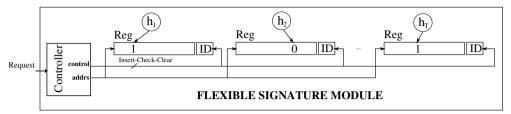

Under this hypothesis, we set up and perform experiments to address these observations and problems. In Chapter 3 we configure a Hardware Transactional Memory (HTM) system where signatures are part of the hardware support and we propose a new hardware filter based on minor modifications of the hardware, which allows a considerable reduction of the signature size either their false positive rate (we call this filter CFM-TM). Under certain circumstances, the performance of the system is also significantly improved. We observe from this work that to optimize the resources and the false positive rate, we require signatures with different sizes.

In Chapter 4 we build the first hardware asymmetric data race detector (which also tolerates these races), called Pacman <sup>1</sup>. Asymmetric data races are a very common type of data race that may cause dangerous concurrent bugs, and that until this work, have only been explored as a software approach. The hardware support of our detector is essentially based on a centralized module of hardware signatures. We demonstrate that Pacman introduces negligible slowdowns in the system, and that it is able to efficiently detect and tolerate asymmetric data races.

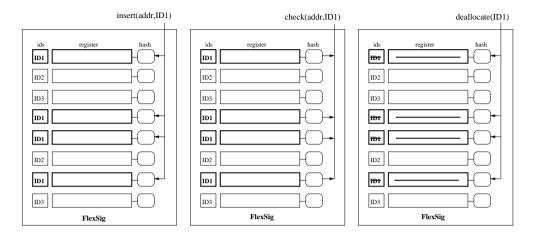

Chapter 5 and Chapter 6 propose a novel hardware signature module (called *FlexSig*) that solves some of the problems that we found when building the previous tools for multicore architectures based on signatures. Specifically, we design a signature module that can host a large number of signatures when there is a high demand of signatures, and it can also achieve

<sup>&</sup>lt;sup>1</sup>This work was developed at the University of Illinois at Urbana-Champaign in collaboration with the members of the I-ACOMA group.

Preface 9

a very low false positive rate when the demand of signatures is modest. We explore several strategies to allocate signatures in *FlexSig* to adapt to the different characteristics of the tools and applications that use them.

Summarizing, we optimized the use of signatures in a HTM system by introducing our CFM-TM filter, we developed a new debugging tool with signatures as main hardware support, and we built a new hardware signature module that allows a great flexibility in the size and number of signatures allocated. This fits in a real scenario represented by a general purpose multicore processor executing a wide range of signature-demanding applications and tools. We have gathered the contributions in the next publications:

Lois Orosa, Javier D. Bruguera, and Elisardo Antelo. A Cache Filtering Mechanism for Hardware Transactional Memory Systems Decoupled from Caches. In *XX Jornadas de Paralelismo*, A Coruña (Spain), September 2009.

Shanxiang Qi, Norimasa Otsuki, Lois Orosa, Abdullah Muzahid, and Josep Torrellas. **Pacman: Tolerating Asymmetric Data Races with Unintrusive Hardware**. In *High Performance Computer Architecture (HPCA)*, 2012 IEEE 18th International Symposium on, pages 1 –12, feb. 2012.

Lois Orosa, Elisardo Antelo, and Javier D. Bruguera. **Flexsig: Implementing Flexible Hardware Signatures**. *ACM Trans. Archit. Code Optim.*, 8(4):30:1–30:20, January 2012.

Lois Orosa, Javier D. Bruguera and Elisardo Antelo. **Asymmetric Allocation in a Flexible Signature Module for Multicore Processors**. *Submitted*.

#### CHAPTER 1

## INTRODUCTION