Conferencia: «Aritmética sobre FPGA a baixo nivel. Aplicación a códigos balanceados»

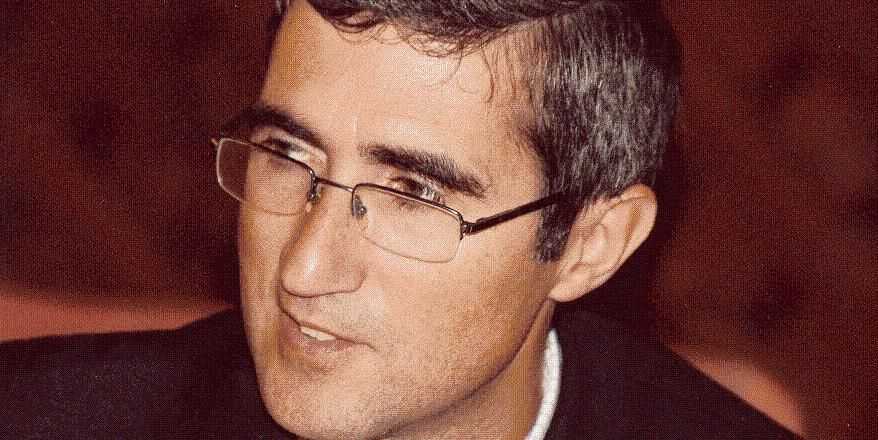

O Dr. Julio Villalba Moreno, Catedrático de Universidade no Departamento de Arquitectura de Computadores da Universidade de Málaga, ofrecerá o próximo xoves unha conferencia no CiTIUS, centrada na súa área de especialización: a aritmética de computadores e arquitecturas especializadas. Actualmente é editor asociado da revista IEEE Transactions on Computers, e membro do comité de programa do IEEE Symposium on Computer Arithmetic.

Resúmen do relatorio

Neste traballo presentamos a estrutura dunha FPGA a baixo nivel. A partir dela, veremos como son implementadas as operacións de suma e multiplicación. Para a suma veremos que se utilizan as LUTs nas que a cadea de carrexos se optimizou para implementar sumadores tipo carrexo enlazado. Para a multiplicación as FPGA de última xeración empregan multiplicadores embebidos.

A continuación tratamos un caso específico: códigos cun número similar de sumas e multiplicacións en coma flotante. É sabido que unha suma en punto flotante implica a realización de desprazamentos para aliñar as mantisas. Esta operación de desprazamento adáptase mal á estrutura dunha FPGA. Por exemplo, en formato IEEE-754 en simple precisión. precísanse de 0 a 24 desprazamentos a nivel de bits, o que consume área e tempo nunha FPGA. A nosa aproximación consiste en usar radix altos para minimizar o número de desprazamentos. O radix alto ten o inconveniente de que aumenta o tamaño dos multiplicadores e o tempo de computación destes. Polo tanto, o que gañamos temporalmente na suma pérdese na multiplicación.

No noso traballo procuramos unha solución de compromiso, que é a utilización de radix 64. Con este valor de radix, conseguimos unha mellora dun 68% en velocidade e redución de área dun 18% para códigos con só sumas, e unha perda dun 20% en velocidade con dobre número de multiplicadores embebidos para códigos de multiplicación pura. Non obstante, para códigos balanceados (número similar de multiplicacións e sumas) obtense unha mellora global do 23% en velocidade. Este resultado é interesante, xa que a maioría das aplicacións en procesado dixital de sinal (DSP) usan filtros dixitais de xeito moi intenso, e os filtros dixitais teñen carga balanceada de multiplicacións e sumas. Polo tanto, todas as aplicacións DSP sobre FPGA se poden beneficiar da arquitectura proposta neste traballo.

O Dr. Julio Villalba Moreno, Catedrático de Universidade no Departamento de Arquitectura de Computadores da Universidade de Málaga, ofrecerá o próximo xoves unha conferencia no CiTIUS, centrada na súa área de especialización: a aritmética de computadores e arquitecturas especializadas. Actualmente é editor asociado da revista IEEE Transactions on Computers, e membro do comité de programa do IEEE Symposium on Computer Arithmetic.

Resúmen do relatorio

Neste traballo presentamos a estrutura dunha FPGA a baixo nivel. A partir dela, veremos como son implementadas as operacións de suma e multiplicación. Para a suma veremos que se utilizan as LUTs nas que a cadea de carrexos se optimizou para implementar sumadores tipo carrexo enlazado. Para a multiplicación as FPGA de última xeración empregan multiplicadores embebidos.

A continuación tratamos un caso específico: códigos cun número similar de sumas e multiplicacións en coma flotante. É sabido que unha suma en punto flotante implica a realización de desprazamentos para aliñar as mantisas. Esta operación de desprazamento adáptase mal á estrutura dunha FPGA. Por exemplo, en formato IEEE-754 en simple precisión. precísanse de 0 a 24 desprazamentos a nivel de bits, o que consume área e tempo nunha FPGA. A nosa aproximación consiste en usar radix altos para minimizar o número de desprazamentos. O radix alto ten o inconveniente de que aumenta o tamaño dos multiplicadores e o tempo de computación destes. Polo tanto, o que gañamos temporalmente na suma pérdese na multiplicación.

No noso traballo procuramos unha solución de compromiso, que é a utilización de radix 64. Con este valor de radix, conseguimos unha mellora dun 68% en velocidade e redución de área dun 18% para códigos con só sumas, e unha perda dun 20% en velocidade con dobre número de multiplicadores embebidos para códigos de multiplicación pura. Non obstante, para códigos balanceados (número similar de multiplicacións e sumas) obtense unha mellora global do 23% en velocidade. Este resultado é interesante, xa que a maioría das aplicacións en procesado dixital de sinal (DSP) usan filtros dixitais de xeito moi intenso, e os filtros dixitais teñen carga balanceada de multiplicacións e sumas. Polo tanto, todas as aplicacións DSP sobre FPGA se poden beneficiar da arquitectura proposta neste traballo.

On-site event

Thursday, November 21, 2013

1384992000000

/events/conferencia-aritmetica-sobre-fpga-a-baixo-nivel-aplicacion-a-codigos-balanceados

events_en